> Требования к курсовому проекту

> Введение - общее описание языка VHDL, краткое описание вышей микросхемы.

> раздел 1. Разработка поведенческой модели микросхемы

> раздел 2. Разработка структурной модели микросхемы

> раздел 3. Разработка потоковой модели микросхемы

> Заключение - чего добились в проекте

Введение- общее описание языка VHDL, краткое описание микросхемы.

Наиболее универсальным и распространенным языком описания аппаратуры является VHDL. На этом языке возможно как поведенческое, так структурное и потоковое описание цифровых схем.

Язык VHDL используется во многих системах для моделирования цифровых схем, проектирования программируемых логических интегральных микросхем, базовых матричных кристаллов, заказных интегральных микросхем.

С точки зрения программиста язык VHDL состоит как бы из двух компонент -общеалгоритмической и проблемно-ориентированной.

Общеалгоритмическая компонента VHDL - это язык, близкий по синтаксису и семантике к современным языкам программирования типа Паскаль, С и др. Язык относится к классу строго типизированных. Помимо встроенных (пакет STANDART) простых (скалярных) типов данных: целый, вещественный, булевский, битовый, данных типа время, данных типа ссылка (указатель) - пользователь может вводить свои типы данных (перечислимый, диапазонный и др.).

Помимо скалярных данных можно использовать агрегаты: массивы array, в том числе и битовые векторы bit_vector, и символьные строки string, записи record, файлы file. Последовательно выполняемые (последовательные) операторы VHDL могут использоваться в описании процессов, процедур и функций. Их состав включает:

- оператор присваивания переменной (:=);

- последовательный оператор назначения сигнала (<=);

- последовательный оператор утверждения (assert);

- условный (if); выбора (case);

- цикла (loop);

- пустой оператор (null);

- оператор возврата процедуры-функции (return);

- оператор последовательного вызова процедуры.

Язык поддерживает концепции пакетного и структурного программирования. Сложные операторы заключены в операторные скобки: if- end if; process- end process; case-end case; loop- end loop и т. д.

Различаются локальные и глобальные переменные. Область "видимости" локальных переменных ограничена пределами блока (процессного, процедурного, оператора блока, оператора описания архитектуры).

Фрагменты описаний, которые могут независимо анализироваться компилятором и при отсутствии ошибок помещаться в библиотеку проекта (рабочую библиотеку), называются пакетами проекта. Такими пакетами могут быть объявление интерфейса объекта проекта entity, объявление архитектуры architecture, объявление конфигурации configuration, объявление интерфейса пакета package и объявление тела пакета package body.

Модули проекта, в свою очередь, можно разбить на две категории: первичные и вторичные. К первичным пакетам относятся объявления пакета, объекта проекта, кон-

фигурации. К вторичным - объявление архитектуры, тела пакета. Один или несколько модулей проекта могут быть помещены в один файл, называемый файлом проекта (design file).

Каждый проанализированный модуль проекта помещается в библиотеку проекта (design library) и становится библиотечным модулем (library unit).

Каждая библиотека проекта в языке VHDL имеет логическое имя (идентификатор). По отношению к сеансу работы с VHDL-системой существует два класса рабочих библиотек проекта: рабочие библиотеки и библиотеки ресурсов.

Рабочая библиотека-это библиотека, с которой в данном сеансе работает пользователь и в которую помещается пакет, полученный в результате анализа пакета проекта.

Библиотека ресурсов - это библиотека, содержащая библиотечные модули, ссылка на которые имеется в анализируемом модуле проекта.

В каждый конкретный момент времени пользователь работает с одной рабочей библиотекой и произвольным количеством библиотек ресурсов.

Модули, как и в обычных алгоритмических языках, - это средство выделения из ряда программ и подпрограмм общих типов данных, переменных, процедур и функций, позволяющее упростить, в частности, процесс их замены.

Так же, как в описаниях проектируемых систем разделяются описания интерфейсов и тел, в VHDL у пакета разделяются описание интерфейса и тела пакета. По умолчанию предусмотрено подключение стандартных пакетов STANDART и TEXT 10. Пакет STANDART, в частности, содержит описание булевских операций над битовыми данными и битовыми векторами. Нестандартные пакеты реализуются пользователями, желающими более точно отобразить свойства описываемых ими объектов. Например, можно в пользовательском пакете переопределить логические операции И, ИЛИ и НЕ и перейти от булевского (О, 1) к многозначному (1, О, X, Z) алфавиту моделирования. Проблемно-ориентированная компонента позволяет описывать цифровые системы в привычных для разработчика понятиях и терминах. Сюда можно отнести:

- понятие модельного времени now;

- данные типа time, позволяющие указывать время задержки в физических единицах;

- данные вида сигнал signal, значение которых изменяется не мгновенно, как у обычных переменных, а с указанной задержкой, а также специальные операции и функции, производимые с этими данными.

Если говорить об операторной части проблемно-ориентированной компоненты, то условно ее можно разделить на средства поведенческого описания аппаратуры (параллельные процессы и средства их взаимодействия); средства потокового описания (описание на уровне межрегистровых передач) - параллельные операторы назначения сигнала (<=) с транспортной transport или инерциальной задержкой передачи сигналов; средства структурного описания объектов (операторы конкретизации компонент с заданием карт портов port map и карт настройки generic map, объявление конфигурации и т. д.).

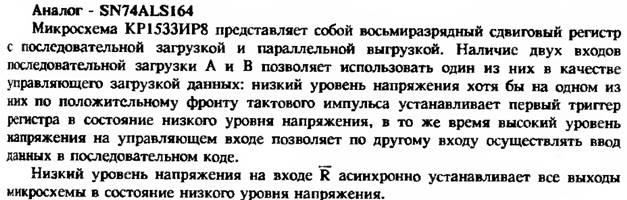

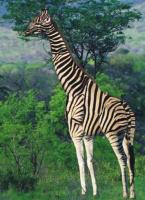

КР1533ИР8

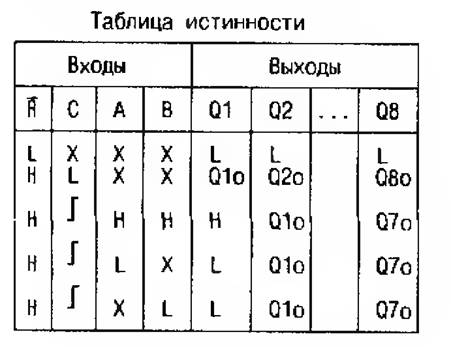

Рис. 1.1 Таблица истинности микросхемы КР1533ИР8

1. Разработка поведенческой VHDL-модели микросхемы

Поведенческая модель описывает отображение входов проекта в выходы, не раскрывая структуру проекта. Благодаря этому свойству поведенческая модель является основным средством формального описания проекта в следующих случаях:

● в начале процесса проектирования, когда составляется абстрактная спецификация на проект и отсутствуют детали его реализации;

● при наличии в проекте частей, представляющих интеллектуальную собственность.

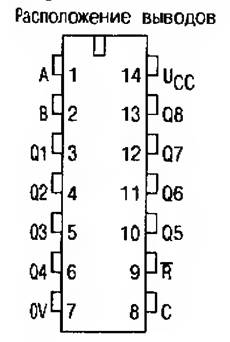

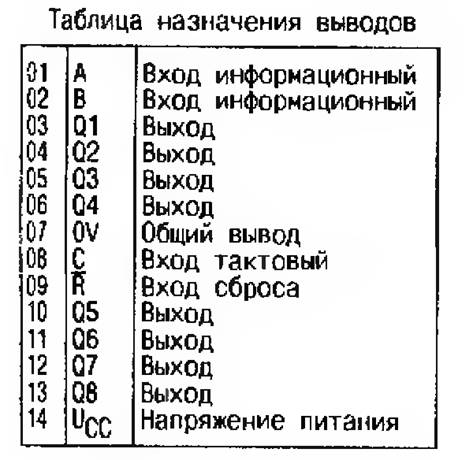

Разработаем поведенческую VHDL-модель микросхемы КР1533ИР8 , условно-графическое изображение которой приведено на рис.1. Микросхема представляет собой два JK-триггера, срабатывающих по отрицательному фронту тактового сигнала и имеющих входы сброса. На рис.1.1 показано расположение всех 14 выводов микросхемы, а назначение каждого из выводов описано в табл.1.1. Информация о выводах служит исходными данными для построения VHDL-модуля entity (рис.1.3), описывающего интерфейс данной микросхемы.

Рис.1.2. Расположение выводов

|

entity KP1533ИР8 is port(R: in Bit; C: in Bit; A: in Bit; B: in Bit; Q1: inout Bit; Q2: inout Bit; Q3: inout Bit; Q4: inout Bit; Q5: inout Bit; Q6: inout Bit; Q7: inout Bit; Q8: inout Bit; end KP1533TB11; |

Рис.1.3. VHDL-модуль entity для микросхемы KP1533ИР8

Интерфейс содержит четыре порта R, C, A, B с режимом in и восемь портов Q1, Q2,Q3,Q4,Q5,Q6,Q7,Q8 с режимом out. Все порты имеют тип Bit. Заметим, что число портов на два меньше числа выводов микросхемы. Порты соответствуют информационным выводам, исключая питание и общий. Для построения модуля использованы зарезервированные слова entity, is, port, in, out, inout, end и разделители ‘(’, ‘:’, ‘;’, ‘:=’, ‘’’, ‘)’.

VHDL-модуль architecture поведенческого уровня строится по табл.1.2, описывающей функционирование триггеров в зависимости от уровней сигналов на их входах.

Таблица 1.2

В табл.1.2 0– низкий уровень сигнала (логический 0), 1 – высокий уровень сигнала (логическая 1), X – безразличное значение, 1/0 - отрицательный фронт сигнала, Q0 – предыдущее значение. Низкий уровень напряжения U0 на входe R устананавливает выходы регистра в нулевое состояние вне зависимости от состояния других входов (С, A и B). При наличии на входe R напряжения высокого уровня U1 то данные, поданные на на входы А и В передвигаются на одну позицию вправо с приходом каждого положительного перепада на тактовый вход С. Причем, запись высокого логического уровня на выход Q1 происходит только при высоком логическом уровне на обоих входах А и В.

VHDL-модуль architecture приведен на рис.1.4. Модуль начинается с зарезервированного слова architecture, за которым следуют имя модуля Behavior, зарезервированное слово of, имя KP1533ИР8 модуля entity. После зарезервированного слова process следует список (R,C,A,B) сигналов, события на которых запускают процесс, вызывая выполнение входящих в него операторов с первого по последний. Вычисление выполняется с помощью условных операторов if, операторов присваивания :=, операции проверки на равенство ‘=’ и логических операций and и not. Положительный фронт на сигнале C моделируется выражением C"Event and C="1", в котором C"Event - атрибут, идентифицирующий событие на сигнале C. Назначение новых состояний выходным портам выполняется с помощью условных операторов if, операторов назначения сигнала <=, операций проверки на равенство ‘=’ и на неравенство ‘/=’ лишь в случае отличия новых состояний от предыдущих. В левой части оператора назначения сигнала указывается имя сигнала. Правая часть включает выражение, определяющее значение сигнала, и после зарезервированного слова after включает выражение, определяющее время (1ps), после которого сигнал получает это значение.

|

architecture Behavior of KP1533ИР8 is begin T: process(R,С,A,B) variable (Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8); begin if R="0" then (Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8)_Temp:="0’; elsif R="1" and C"Event and C1="1" then if A="1" and B="1" then Q8<="Q7" after 1ps; Q7<="Q6" after 1ps; Q6<="Q5" after 1ps; Q5<="Q4" after 1ps; Q4<="Q3" after 1ps; Q3<="Q2" after 1ps; Q2<="Q1" after 1ps; Q1<="1" after 1ps; elsif A="0" or B="0" or (A="1" and B="1") then Q8<="Q7" after 1ps; Q7<="Q6" after 1ps; Q6<="Q5" after 1ps; Q5<="Q4" after 1ps; Q4<="Q3" after 1ps; Q3<="Q2" after 1ps; Q2<="Q1" after 1ps; Q1<="0" after 1ps; end if; end if; end process T; |

Рис.1.4. VHDL-модуль architecture

Среда тестирования (Test_Bench) создается как отдельный объект проекта на языке VHDL (рис.1.5). Все сигналы, воздействующие на тестируемый модуль, представленный VHDL-модулями KP1533ИР8 и Behavior, генерируются внутри среды, поэтому VHDL-модуль entity среды с именем KP1533ИР8_T не включает параметров настройки и портов. Архитектура среды тестирования (VHDL-модуль architecture с именем TB_Architecture) построена на смешанном структурно-потоковом уровне. Тестируемый модуль объявлен как компонент (component) с именем KP1533ИР8 и двенадцатью формальными портами. Объявление компонента используется для определения одной его копии с именем UUT посредством параллельного оператора конкретизации компонента, входящего в исполнительную часть модуля architecture среды тестирования. Оператор конкретизации включает отображение формальных портов (portmap) компонента на фактические одноименные сигналы R, C, A, B, Q1…Q8, объявленные в разделе объявлений архитектуры TB_Architecture. Все порты и сигналы имеют тип Bit. Входные сигналы, для которых порты имеют режим in, inout, являются внешними стимулами для тестируемого модуля и генерируются вне его. Они генерируются, за исключением сигналов C в модуле T_Architecture посредством параллельных операторов назначения сигнала. Правая часть оператора содержит последовательность разделенных запятой транзакций, описывающих будущую временную диаграмму для сигнала, имя которого составляет левую часть оператора. Каждая транзакция представляется парой выражений. Первое выражение определяет значение сигнала. Второе выражение, стоящее после зарезервированного слова after, определяет время, через которое, начиная с текущего момента веремени, сигнал получит значение. Второй элемент пары может опускаться, время в этом случае принимается равным нулю. Например, в результате выполнения оператора R<="1", "0" after 400ns, "0" after 400ns; сигнал R сначала получит значение "1", через 400ns получит значение "0", а через 400ns от текущего момента времени снова получит значение "1". Таким образом, операторы назначения сигнала устанавливают последовательность событий на каждом сигнале. Для генерации тактирующих сигналов C используется специальное средство среды Active-VHDL. Это средство позволяет определить временные диаграммы сигналов. Сигналы периодически изменяют значение с ‘0’ на ‘1’ и с ‘1’ на ‘0’, причем время цикла составляет 50ns, что обеспечивает частоту 20MHz. На протяжении 50% времени значение сигнала равно ‘0’ и на протяжении 50% времени значение равно ‘1’. VHDL-модуль configuration связывает копию UUT компонента KP1533ИР8 с объектом проекта, представленным интерфейсом KP1533ИР8 и архитектурным телом Behavior.

События на входных сигналах определяют порядок перезапуска процессов, моделирующих работу регистра. Процессы, в свою очередь, вычисляют временные диаграммы для сигналов Q1..Q8.

|

entity KP1533ИР8_T is end KP1533TBИР8_T; architecture TB_Architecture of КР1533ИР8_t is -- Component declaration of the tested unit component KP1533ИР8 port(R : in Bit; C : in Bit; A : in Bit; B : in Bit; Q1 : out Bit; Q2 : out Bit; Q3 : out Bit; Q4 :out Bit; Q5 : out Bit; Q6 : out Bit; Q7 : out Bit; Q8 : out Bit;) end component; --Stimulus signals - signals mapped to the --input and inout ports of tested entity signal R : Bit; signal C : Bit; signal A : Bit; signal B : Bit; signal Q1 : Bit; signal Q2 : Bit; signal Q3 : Bit; signal Q4 : Bit; signal Q5 : Bit; signal Q6 : Bit; signal Q7 : Bit; signal Q8 : Bit; |

begin --Unit Under Test port map UUT : KP1533ИР8 port map(R => R, C => C, A => A, B => B, Q1 => Q1, Q2 => Q2, Q3 =>Q3, Q4 => Q4, Q5 => Q5, Q6 => Q6, Q7 => Q7, Q8 => nQ2); R<="1", "0" after 400ns, "0" after 400ns; A<="1", "0" after 30ns, "1" after 30ns, "0" after 30ns; B<="1", "0" after 60ns; C<="0", "1" after 25ns, "0" after 25ns; end TB_Architecture; configuration Testbench_for_KP1533ИР8 of KP1533ИР8_T is for TB_Architecture for UUT : KP1533ИР8 use entity work.KP1533ИР8 (Behavior); end for; end for; end Testbench_for_KP1533ИР8; |

Рис.1.5. Среда тестирования поведенческой модели

2. Разработка структурной VHDL-модели микросхемы

Структурная модель описывает состав компонентов проекта, типы компонентов, соединения выходов одних компонентов с входами других. Благодаря этому свойству структурная модель является основным средством формального детального описания проекта в следующих случаях:

● в конце процесса проектирования, когда строится или генерируется детальное описание проекта, представляющее собой реализацию исходной спецификации поведенческого уровня;

● при иерархической многоуровневой декомпозиции сложного проекта на части, представленные в свою очередь на структурном уровне, либо представленные на поведенческом или потоковом уровне.

Разработаем структурную VHDL-модель микросхемы КР1533ИР8, функциональная схема которой представлена на рис.2.1. На рис. 2.2 представляем функциональную схему D-триггера, как основной функциональной составляющей микросхемы регистра.

Функциональная схема состоит из логических элементов: буферный логический элемент НЕ-НЕ, инвертор логического сигнала- элемент НЕ, один двухвходовый элемент И, восемь D-триггеров. Большинство связей между элементами являются прямыми. Обратные связи направлены от выходов триггеров младших разрядов к D-входам триггеров следующего разряда. Рассматриваем функциональную схему для одного D-триггера

(один разряд регистра), который включает в себя 6 логических элементов 3И-НЕ.

Структурная VHDL-модель микросхемы представлена на рис.2.3. Это VHDL-модуль architecture структурного уровня. Уровень модуля опеределяется наличием в нем таких типично «структурных» конструкций, как объявление компонента и конкретизация компонента. Объявление выполняется для каждого нового типа компонента. Конкретизация выполняется для каждой отдельной копии компонента в структуре. В рассматриваемую микросхему входят пять типов и шестнадцать копий компонентов. Типы компонентов именуются идентификаторами Not_Not, Not, And2, And3_Not. Копии компонентов именуются идентификаторами Comp1,…,Comp9. Связи между входами и выходами копий компонентов представляются сигналами

Рис. 2.1 Функциональная схема микросхемы КР1533ИР8

Рис. 2.2 Функциональная схема D-триггера.

|

architecture Structure of KP1533ИР8 is component Not_Not port(A:in Bit; Y:out Bit); end component; component Not port(A:in Bit; Y:out Bit); end component; component And2 port(A,B:in Bit; Y:out Bit); end component; component And3_Not port(A,B,C:in Bit; Y:out Bit); end component; signal s1,s2,s3,s4,s5,s6,s8,s9: Bit; signal S: Bit:="1"; begin Comp1:Not_Not port map(R,s1); Comp2:Not port map(C,s2); Comp3:And2 port map(A,B,s3); Comp4:And3_Not port map (S,s5,s7,s4); Comp5:And3_Not port map(s4,s1,s2,s5); Comp6:And3_Not port map(s5,S,s7,s6); Comp7:And3_Not port map(s6,s1,s3,s7); Comp8:And3_Not port map(S,s5,s9,s8); Comp9:And3_Not port map(s8,s1,S6,s9); Q1<=s8; end Structure; Рис.2.3. Структурная VHDL-модель одного разряда микросхемы |

entity Not_Not is port(A:in Bit; Y:out Bit); end Not_Not; architecture DF_Not_Not of Not_Not is begin Y <= not A not ; end DF_Not_Not; entity Not is port(A:in Bit; Y:out Bit); end Not; architecture DF_Not of Not is begin Y<=not A ; end DF_Not; entity And2 is port(A,B:in Bit; Y:out Bit); end And2; architecture DF_And of And is begin Y<=(A and B) after 1ps; end DF_And; entity And3_Not is port(A,B,C:in Bit; Y:out Bit); end And3_Not; architecture DF_And3_Not of And3_Not is begin Y<= not (A and B and C) after 2ps; end DF_And3_Not; |

Рис.2.4. VHDL-модели компонентов структуры

Объявление компонента начинается с зарезервированного слова component, за которым следует имя компонента. Далее объявляются формальные параметры настройки (generic) и порты (port) компонента. Для каждого указываются имя, режим (in, out, inout) и тип или подтип. Объявление заканчивается парой зарезервированных слов endcomponent. Так, третий объявляемый компонент имеет имя And2 и формальные порты A, B, Y. Все порты имеют тип Bit. Первые два являются входными (режим in), третий – выходным (режим out). За объявлением компонентов следует объявление сигналов, используемых для представления связей между входами и выходами компонентов. В рассматриваемой структурной модели связи представляются сигналами s1,…,s9. Объявление сигналов начинается с зарезервированного слова signal, за которым следуют имена сигналов, их тип Bit. Начальное значение сигналов устанавливается по умолчанию. Им является первое значение перечислимого типа Bit, т.е. значение ‘0’.

Конкретизация компонента начинается с определения имени для копии компонента. За именем копии через символ ‘:’ следует имя компонента, введенное в его объявлении. Описание отображения параметров настройки начинается зарезервированными словами genericmap, отображения портов – зарезервированными словами portmap. Параметры настройки являются для компонента константами, порты – сигналами. Отображение назначает формальным параметрам или портам фактические константы или сигналы, объявленные за пределами компонента. Назначение может быть позиционным, ключевым или смешанным. Позиционное назначение использовано при конкретизации компонента Comp1.

Компонентам архитектурного тела структурного уровня ставятся в соответствие объекты проекта следующего уровня иерархии. Соответствие устанавливается с помощью VHDL-модуля configuration. Каждый объект описывается двумя модулями: модулем entity и модулем architecture. Имена модулей отличаются в общем случае от имени, используемом в объявлении компонента. Имена параметров настройки и портов модуля entity также отличны (но не обязательно) от имен формальных параметров и портов компонента. Проиллюстрируем сказанное на примере. Компоненту с именем And3_Not, объявленному в архитектуре с именем Structure, ставятся в соответствие одноименный модуль entity и модуль architecture с именем DF_And3_Not. Формальные порты A, B, C, D, Y компонента совпадают по имени с фактическими портами модуля entity. Соответствие между формальными и фактическими портами позиционное. Модуль architecture включает единственный параллельный оператор назначения сигнала, устанавливающий в качестве значения выходного порта Y значение выражения not(A and B and C and D) после 2ps.

3. Разработка потоковой VHDL-модели микросхемы

Потоковая модель является промежуточной между поведенческой и структурной моделями. С одной стороны, она не определяет состав компонентов, входящих в проект, и связи между ними. С другой стороны, описываемое ею поведение не является полностью абстрактным, но в той или иной степени отражает детали структуры проекта. Названием модель обязана представляемому ею способу обработки информации: это поток данных. Модель строится как множество параллельных асинхронно функционирующих взаимодействующих процессов. Связи между процессами устанавливаются посредством сигналов. Изменение значений сигналов, вызванное одними процессами, приводит к запуску других процессов. Те в свою очередь воздействуют на третьи процессы, и так далее. Благодаря свойству потоковости модель является основным средством формального описания проекта в процессе автоматического синтеза, базирующегося на использовании высокоуровневых языков описания аппаратуры.

Разработаем потоковую VHDL-модель микросхемы КР1533ИР8, функциональная схема которой представлена на рис.2.1, а на рис.3.1 представлена ее структурная VHDL-модель. Для всех внутренних соединений схемы введем локальные сигналы и выразим одни сигналы через другие, воспользовавшись параллельными операторами назначения сигнала (рис.3.1). Левая часть оператора содержит имя сигнала, будущая временная диаграмма которого определяется правой частью оператора. Правая часть состоит из последовательности транзакций, каждая из которых записывается в виде V after T и состоит из двух частей: выражения V, определяющего значение сигнала, и выражения T, определяющего время, через которое сигнал получит это значение. В процессе компиляции VHDL-модели, каждый параллельный оператор назначения сигнала автоматически трансформируется в отдельный оператор process, имя которого совпадает с именем оператора назначения сигнала (если такое имеется). В список чувствительности процесса включаются имена всех сигналов, входящих в правую часть оператора назначения. В исполнительную часть процесса включается один последовательный оператор назначения сигнала, который в отношении левой части и транзакций копирует исходный параллельный оператор. Заметим, если исходный оператор является условным или селективным, то в исполнительную часть процесса включаются также условые операторы if или селективный оператор case. Далее процесс со списком чувствительности трансформируется в процесс без такого списка, при этом в конец исполнительной части вставляется последовательный оператор ожидания.

Так, параллельный оператор назначения сигнала|

architecture Data_Flow of KP1533ИР8 is signal s1,s2,s3,s4,s5,s6,s8,s9: Bit; begin s1 <= not (not R) after 2ps s2 <= not (C) after 2ps; s3 <=A and B after 2ps; s4 <= not (S and s7 and s5) after 2ps ; s5 <= not (s4 and s1 and s2) after 2ps ; s6 <= not (s5 and s2 and s7) after 2ps; s7 <= not (s6 and s1 and s3) after 2ps; s8 <= not (S or s5 or s9) after 1ps; s9 <= not (s8 or s1 or s6) after 1ps; end Data_Flow; |

Рис.3.1. Потоковая VHDL-модель микросхемы

Имитационное моделирование потоковой VHDL-модели выполнено в той же среде тестирования, что и имитационное моделирование поведенческой и структурной VHDL-моделей.

Заключение

В процессе работы над представленным курсовым проектом были изучены основы языка программирования VHDL, его операторы, процессы, процедуры и функции. С помощью языка VHDL было проведено описание логической интегральной микросхемы К1533ИР8, включившее в себя разработку поведенческой модели микросхемы, структурной модели микросхемы и потоковой модели микросхемы.

(zip - application/zip)

(zip - application/zip)