Министерство образования и науки РФ

Северо-Кавказский горно-металлургический институт

(Государственный технологический университет)

Факультет Электронной техники

Кафедра Промышленная электроника

Курсовой проект

по дисциплине

Основы проектирования электронных компонентов базы

на тему:

«Проектирование электронного компонента»

Выполнил:

ст-т гр. Энб-13-3

Макоев Х.О.

Проверил:

Маслаков М.П.

Владикавказ 2016

Содержание

|

Задание |

|

|

Введение |

|

|

1 Суммирующий двоичный счетчик с последовательным переносом, собранный на Т-триггерах………………………………………………........ |

5 |

|

1.1Двоичные счетчики………………………………………………….. |

5 |

|

1.2 Двоичные счетчики с параллельным переносом………………….. |

5 |

|

1.3 Счетчики с последовательно-параллельным переносом…………. |

7 |

| 2 Комбинационная схема…………………………………………………….. |

10 |

|

2.1 Построение комбинационной схемы………………………………. |

11 |

| 3 Параллельный регистр, собранный на RS-триггерах…………………….. |

13 |

|

4 Неполный дешифратор с активными единичными сигналами на выходе |

16 |

|

5 Сборка нового элемента…………………………………………………… |

20 |

|

Заключение……………………………………………………………………. |

22 |

|

Список использованной литературы………………………………………... |

23 |

Вариант №49

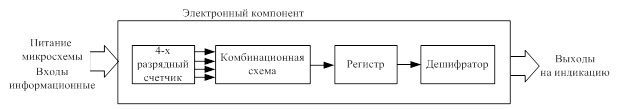

Собрать принципиальную электрическую схему по следующей структурной схеме:

Где:

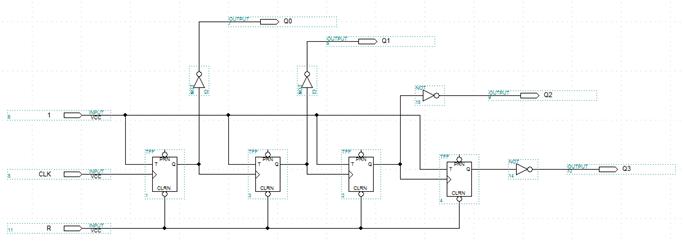

1. Счетчик - суммирующий двоичный счетчик с последовательным переносом, собранный на T-триггерах.

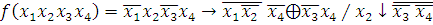

2. Комбинационная схема – построена на основе ДСНФ или КСНФ (если в ДСНФ элементов больше, чем в КСНФ строить на основе нее, если меньше, то на основе КСНФ) по следующей функции:

3. Регистр – параллельный регистр, собранный на RS-триггерах.

4. Дешифратор – не полный дешифратор с активными единичными сигналами на выходе.

Произвести моделирование схемы, сняв характеристики работы, и представить в виде завершенного электронного компонента, полученного в САПР МАХ+ (микросхема).

Принципиальная схема, принципиальная электрическая схема -графическое изображение (модель), служащее для передачи с помощью условных графических и буквенно-цифровых обозначений (пиктограмм) связей между элементами электрического устройства.

Принципиальные электрические схемы определяют полный состав приборов, аппаратов и устройств (а также связей между ними), действие которых обеспечивает решение задач управления, регулирования, защиты, измерения и сигнализации. Принципиальные схемы служат основанием для разработки других документов проекта: монтажных таблиц щитов и пультов, схем внешних соединений и др.

1 Суммирующий двоичный счетчик с последовательным переносом, собранный на Т-триггерах.

1.1 Двоичные счетчики

Схему двоичного счетчика можно получить с помощью формального синтеза, однако более наглядным путём представляется эвристический. Таблица истинности двоичного счетчика — последовательность двоичных чисел от нуля до 2^n-1, где n - разрядность счётчика. Наблюдение за разрядами чисел, составляющих таблицу, приводит к пониманию структурной схемы двоичного счетчика. Состояния младшего разряда при его просмотре по соответствующему столбцу таблицы показывают чередование нулей и единиц вида 01010101..., что естественно, т. к. младший разряд принимает входной сигнал и переключается от каждого входного воздействия. В следующем разряде наблюдается последовательность пар нулей и единиц вида 00110011... . В третьем разряде образуется последовательность из четверок нулей и единиц 00001111... и т.д. Из этого наблюдения видно, что следующий по старшинству разряд переключается с частотой, в два раза меньшей, чем данный.

Известно, что счетный триггер делит частоту входных импульсов на два. Сопоставив этот факт с указанной выше закономерностью, видим, что счетчик может быть построен в виде цепочки последовательно включенных счетных триггеров.

1.2 Двоичные счетчики с параллельным переносом

Выше рассмотрены схемы двоичных последовательных счетчиков, то есть таких счетчиков, в которых при изменении состояния определенного триггера возбуждается последующий триггер, причем триггеры меняют свои состояния не одновременно, а последовательно. Если в данной ситуации должны изменить свои состояния n триггеров, то для завершения этого процесса потребуется n интервалов времени, соответствующих времени изменения состояния каждого из триггеров. Такой последовательный характер работы является причиной двух недостатков последовательного счетчика: меньшая скорость счета по сравнению с параллельными счетчиками и возможность появления ложных сигналов на выходе схемы. В параллельных счетчиках синхронизирующие сигналы поступают на все триггеры одновременно.

Последовательный характер переходов триггеров счетчика является источником ложных сигналов на его выходах. Например, в счетчике, ведущем счет в четырёхразрядном двоичном коде с «весами» 8-4-2-1, при переходе от числа 7_{10} = 0111_2 к числу 8_{10} = 1000_2 на выходе появится следующая последовательность сигналов:

0111 ->ð 0110 ->ð 0100 ->ð 0000 ->ð 1000

Это означает, что при переходе из состояния 7 в состояние 8 на входах счетчика на короткое время появятся состояния 6; 4; 0. Эти дополнительные состояния могут вызвать ложную работу других устройств, например, если к такому счетчику подключён дешифратор, то на его выходах 0, 4, 6 могут кратковременно возникнуть активные состояния, которые могут ложно изменить состояния подключенных к ним триггеров — это явление называется логическими «гонками» или «гонками сигналов». Исключить гонки можно, применяя счетчики с соседним или противогоночным кодированием состояний, например, считающие в рефлексивном коде Грея.

С целью уменьшения времени протекания переходных процессов можно реализовать счетчик в варианте с подачей входных импульсов одновременно на все триггеры. В этом случае получим счетчик с параллельным переносом.

По схемам счетчиков всегда строятся счетчики, задержка переключения одного триггера у которых соизмерима с периодом считаемых импульсов. Пример. Задержка переключения одного триггера 30 нс, и если мы построим счетчик более, чем 4-хразрядный, то при периоде счетных импульсов 120 нс могут начаться сбои счета, перенос не успевает распространиться по цепочке триггеров до прихода очередного счетного импульса.

Здесь на информационные входы триггеров подаются сигналы, являющиеся логической функцией состояния счетчика и определяющие конкретные триггеры, которые изменяют своё состояние при данном входном импульсе. Принцип стробирования сводится к следующему: триггер меняет своё состояние при пропускании очередного импульса синхронизации, если все предыдущие триггеры находились в состоянии логической единицы.

Параллельные счетчики имеют более высокое быстродействие по сравнению с последовательными, поскольку синхронизирующие импульсы поступают на все триггеры одновременно.

1.3 Счетчики с последовательно-параллельным переносом

В связи с ограничениями на построение счетчиков с параллельным переносом большой разрядности широкое распространение получили счетчики с групповой структурой, или счетчики с последовательно-параллельным переносом. Разряды таких счетчиков разбиваются на группы, внутри которых организуется принцип параллельного переноса. Сами же группы соединяются последовательно с использованием конъюнкторов, формирующих перенос в следующую группу при единичном состоянии всех триггеров предыдущих. При единичном состоянии всех триггеров группы приход очередного входного сигнала создаст перенос из этой группы. Эта ситуация подготавливает межгрупповой конъюнктор к прямому пропусканию входного сигнала на следующую группу.

В наихудшем для быстродействия случае, когда перенос проходит через все группы и поступает на вход последней,

tУСТ = t • (ĺ — 1) + tГР,

где ĺ — число групп, tГР — время установления кода в группе.

В развитых сериях ИС обычно имеется по 5…10 вариантов двоичных счетчиков, выполненных в виде 4-хразрядных групп (секций). Каскадирование секций может выполняться путём их последовательного включения по цепям переноса, организации параллельно-последовательных переносов или для более сложных счетчиков с двумя дополнительными управляющими входами разрешения счета и разрешения переноса путём организации параллельных переносов и в группах, и между ними.

Особенностью двоичных счетчиков синхронного типа является наличие ситуаций с одновременным переключением всех его разрядов (например, для суммирующего счетчика при переходе от кодовой комбинации 11…1 к комбинации 00…0 при переполнении счетчика и выработке сигнала переноса). Одновременное переключение многих триггеров создает значительный токовый импульс в цепях питания ЦУ и может привести к сбою в их работе. Поэтому в руководящих материалах по использованию некоторых БИС/СБИС программируемой логики, в частности, имеется ограничение на разрядность двоичных счетчиков заданной величиной k. При необходимости применения счетчика большей разрядности рекомендуется переходить к коду Грея, для которого переходы от одной кодовой комбинации к другой сопровождаются переключением всего одного разряда. Правда, для получения результата счета в двоичном коде придется использовать дополнительно преобразователь кода, но это является платой за избавление от токовых импульсов большой интенсивности в цепях питания.

Счётчики с последовательным переносом, это счётчики, в которых переключение триггеров разрядных схем осуществляется последовательно один за другим.

Рисунок 1 - Схема суммирующего двоичного счетчика с последовательным переносом, собранного на Т-триггерах

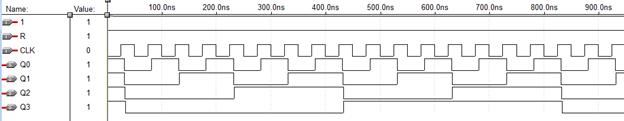

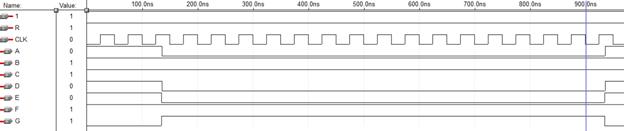

Рисунок 2 - Временные диаграммы, характеризующие работу счетчика

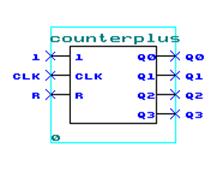

Рисунок 3 - Графическое изображение полученной модели счетчика

2 Комбинационная схема

Комбинационные схемы - это схемы, у которых выходные сигналы Y = (у1, у2, ..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2,..., хn), поступающих в тот же момент времени t. Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y=f(Х). Логические функции и соответствующие им комбинационные схемы подразделяют на регулярные и нерегулярные структуры. Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими. В нерегулярных структурах такая аналогия отсутствует. Многие регулярные структуры положены в основу построения отдельных ИС малой и средней степени интеграции или отдельных функциональных частей БИС и СБИС. Из регулярных комбинационных схем наиболее распространены дешифраторы, шифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы и др.

Для построения любой КС необходима таблица истинности ее функционирования (составляется или задается), затем составляется функция зависимости каждого выхода схемы от входа (в форме СДНФ, которую затем можно перевести в упрощенную форму) и производится построение схемы на определенных логических элементах (чаще всего на И-НЕ и ИЛИ-НЕ). Как правило, построение и расчет любой схемы осуществляется, начиная с ее выхода.

2.1 Построение комбинационной схемы

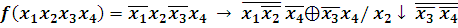

;

;

Таблица 1 – Таблица истинности для

функции  .

.

|

x1 |

x2 |

x3 |

x4 |

a |

b |

c |

d |

e |

f |

g |

h |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

a= ;

;

b= ;

;

c= ;

;

d= ;

;

e= ;

;

f= ;

;

g= ;

;

h= ;

;

Так как ложных значений у функции больше, чем истинных, то находим КСНФ и по ней строим комбинационную схему.

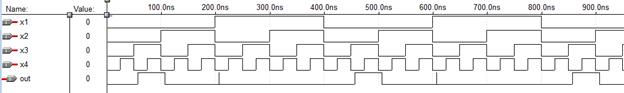

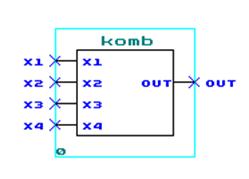

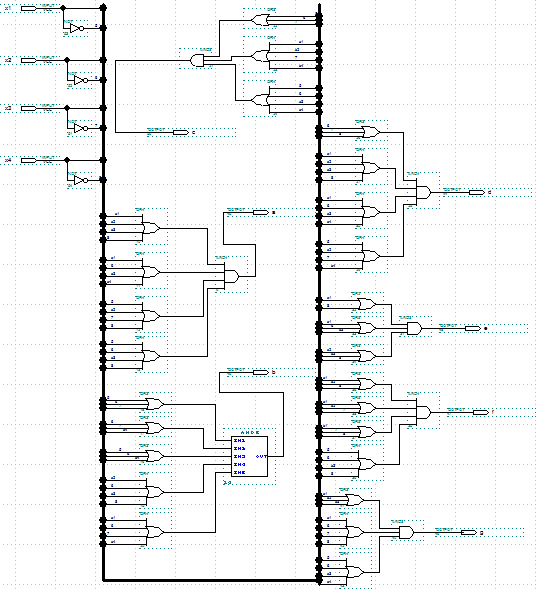

Рисунок 4 - Комбинационная схема

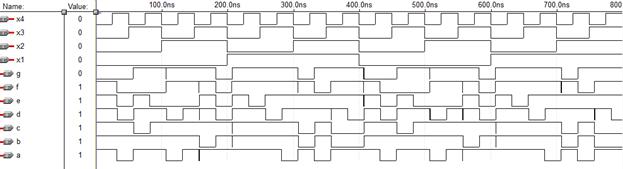

Рисунок 5 - Временные диаграммы, характеризующие работу комбинационной схемы

Рисунок 6 - Графическое изображение полученной модели комбинационной схемы

3 Параллельный регистр, собранный на RS-триггерах

Регистр - устройство для хранения и (или) преобразования многоразрядных чисел.

Регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки.

Элементами структуры регистров являются синхронные триггеры D, RS или JK - типа с динамическим или статическим управлением. Так как одиночный триггер может запомнить один разряд (бит) двоичной информации, то его можно считать одноразрядным регистром. Для запоминания многоразрядных чисел используют "линейки " из нескольких триггеров - по количеству разрядов чисел. В схемы регистров входят также комбинационные элементы, роль которых в данном случае вспомогательная.

Занесение информации в регистр называют операцией ввода или считывания. Запись информации в регистр не требует его предварительного обнуления (сброса).

Все регистры в зависимости от функциональных свойств подразделяются на две категории: накопительные регистры (памяти, хранения) и сдвиговые.

Регистры памяти - простейший вид регистров. Их задача - хранить двоичную информацию небольшого объема в течение короткого промежутка времени. Эти регистры представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись, загрузка) и вывод (считывание) информации производится одновременно во всех разрядах параллельным кодом. Запись обеспечивается тактовым импульсом. С приходом очередного тактового импульса происходит обновление записанной информации.

Сигналы на выходах триггеров характеризуют выходную информацию. Считывание может производиться в прямом или в обратном коде (в последнем случае - с инверсных выходов). Регистры памяти (хранения) представляют собой, по существу, наборы триггеров с независимыми информационными входами и (обычно) общим тактовым входом. В качестве регистров подобного рода могут быть использованы без дополнительных элементов многие типы синхронных триггеров.

Особенно пригодны микросхемы, содержащие в одном корпусе несколько самостоятельных триггеров.

Кроме операции хранения данных регистры могут использоваться и для операции сдвига данных с целью преобразования двоичного последовательного кода в параллельный и наоборот. Это так называемые сдвиговые регистры или регистры сдвига, которые получаются путем цепочного соединения триггеров.

Суть сдвига состоит в том, что по сигналу синхроимпульса происходит одновременная перезапись содержимого каждого триггера в соседний триггер. При этом не меняется само двоичное слово (число), записанное в регистре, оно лишь сдвигается на один разряд и только содержимое последнего триггера ТТ3 пропадает из регистра, а на вход первого ТТ0 поступает новый бит.

Параллельные регистры - это устройства, предназначенные для записи, хранения и выдачи информации, представленной в виде двоичных кодов. Для хранения каждого двоичного разряда в регистре используется одна триггерная ячейка.

Для запоминания многоразрядных слов необходимое число триггеров объединяют вместе и рассматривают как единый функциональный узел-регистр. Если регистр построен на триггерах-защелках, то его называют регистр-защелка.

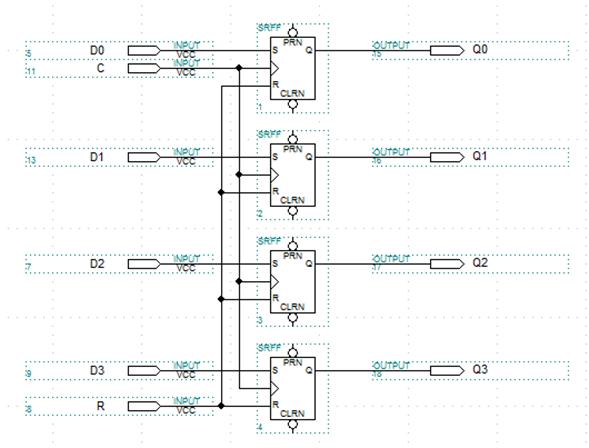

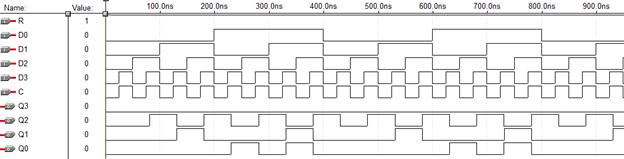

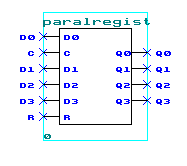

Рисунок 7 - Параллельный регистр, собранный на RS-триггерах

Рисунок 8 - Временные диаграммы, характеризующие работу регистра

Рисунок 9 - Графическое изображение полученной модели регистра

4 Неполный дешифратор с активными единичными сигналами на выходе

Дешифратор - устройство для расшифровки (декодирования) сообщения и перевода содержащейся в нём информации на язык (в код) воспринимающей системы. В общем случае дешифратор имеет n входов и m выходов. Поступающая на входы дешифратор информация преобразуется — дешифрируется, — и на соответствующем выходе (группе выходов) выделяется сигнал, указывающий признак (или содержание) входной информации. Любому сигналу или комбинации сигналов на входах дешифратор соответствует определённый сигнал или комбинация сигналов на выходах дешифратор Это соответствие задаётся структурой дешифратор при его проектировании. дешифратор. применяют в различных устройствах обработки и передачи информации: в телемеханике, в вычислительной технике (декодирующие устройства, преобразователи представления величин), в радиотехнике и измерительной технике (Детекторы, демодуляторы), в системах телефонной и телеграфной связи. Назначение предопределяет структуру, число входов и выходов дешифратор, форму и последовательность входных и выходных сигналов.

Дешифратор в телемеханике расшифровывают сообщения (их коды) по структурам принимаемых сигналов. Структура сигналов создаётся приданием импульсам, образующим сигналы, различных качеств — признаков. Такими признаками являются полярность, частота и порядок следования, количество, длительность и амплитуда импульсов, группировка импульсов различного качества и т.д. Если, например, дешифратор используется в системе телеуправления, то дешифратор автоматически анализирует структуру принимаемых сигналов в соответствии с программой, заложенной в конструкции самого дешифратор; сигналы с его выходов подаются на входы исполнительных механизмов управляемых объектов. Избирательность — основное свойство дешифратор; она обеспечивает защиту входных цепей воспринимающих систем от посторонних сигналов, которые могут оказать ложное воздействие на систему.

В вычислительной технике дешифратор применяют в качестве преобразователей кода в код или кодов в эквивалентные им непрерывные величины. В радиотехнике дешифратор. восстанавливает передаваемое сообщение из радиосигнала, параметры которого изменяются в такт с передаваемым сообщением.

Таблица 2 - Таблица истинности работы дешифратора

|

x1 |

x2 |

x3 |

x4 |

a |

b |

c |

d |

e |

f |

g |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

Рисунок 10 - Неполный дешифратор

Рисунок 11 - Временные диаграммы, характеризующие работу дешифратора

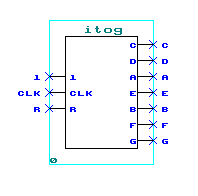

Рисунок 12 - Графическое изображение полученной модели дешифратора

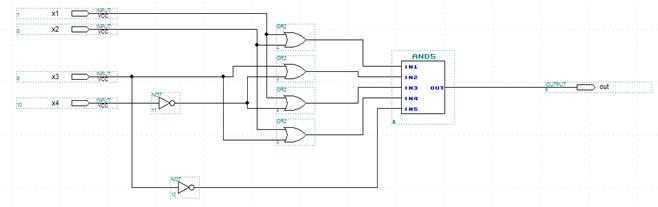

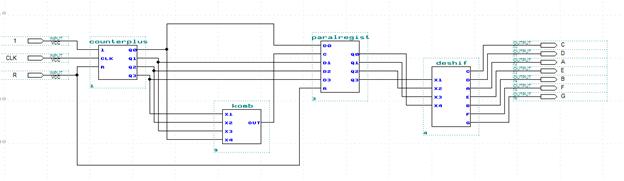

5 Сборка нового элемента

В этом пункте производится окончательная сборки схемы путем соединения ранее полученных компонентов. От источника сигналов «1» будет поступать напряжение высокого уровня необходимое для нужной работы счетчика и регистра. Счетчик будет производить подсчет импульсов поступающих на его вход «CLK» от источника. Полученный четырехразрядный код будет поступать на входы регистра и комбинационной схемы, с выхода которой сигнал также поступает на вход регистра. Информационные коды поступающие на вход регистра сохраняются и передаются на вход дешифратора, где преобразуются в сигнал высокого уровня на выходе, номер, которого соответствует десятичному значению поступившего кода.

Рисунок 13 - Схема нового элемента

Рисунок 14 - Временные диаграммы, характеризующие работу нового элемента

Рисунок 15 - Графическое изображение полученной модели нового элемента

Заключение

В ходе выполнения курсового проекта мною была собрана принципиальная электрическая схема состоящая из: суммирующего двоичного счетчика, комбинационной схемы, параллельного регистра и дешифратора.

Были получены знания о работе компонентов используемых в схеме. Так же была освоена программа проектирования устройств на ПЛИС Altera MAX+PLUS II и рассмотрены основные методы построения схем из уже имеющихся в библиотеке компонентов.

Список использованной литературы

1 Потехин Д.С., Тарасов И.Е., «Разработка систем цифровой обработки сигналов на базе ПЛИС», г. Москва, 2007г.

2 Поляков А.К., «Языки VHDL и Verilog в проектировании цифровой аппаратуры на ПЛИС. Учебное пособие для вузов», г. Москва, 2012г.

3 Антонов А.П., «Язык описания цифровых устройств. ALTERA HDL. Практический курс», г. Москва, 2002г.

4 Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П., «Проектирование систем на микросхемах программируемой логики», г. Санкт-Петербург, 2002г.

5 Зобенко А. А., Филиппов А. С., Комолов Д. А., Мяльк Р. А., «Системы автоматизированного проектирования фирмы Altera MAX+plus II и Quartus II. Краткое описание и самоучитель», г. Москва, 2002 г.

(zip - application/zip)

(zip - application/zip)