Министерство образования и науки РФ

Северо-Кавказский горно-металлургический институт

(Государственный технологический университет)

Факультет Электронной техники

Кафедра Промышленная электроника

Курсовой проект

по дисциплине

Основы проектирования ЭКБ

на тему:

Проектирование электронного компонента в САПР Altera

Выполнил:

ст-т гр. ЭМб-12-__

________________

Проверил:

Маслаков М.П.

Владикавказ 201__

Содержание

Задание. 3

Введение. 4

1.Суммирующий двоичный счетчик с последовательным переносом, собранный на D-триггерах. 7

2.Комбинационная схема. 9

2.1.Построение комбинационной схемы по функции. 10

3.Параллельный регистр, собранный на D-триггерах. 13

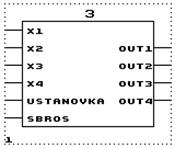

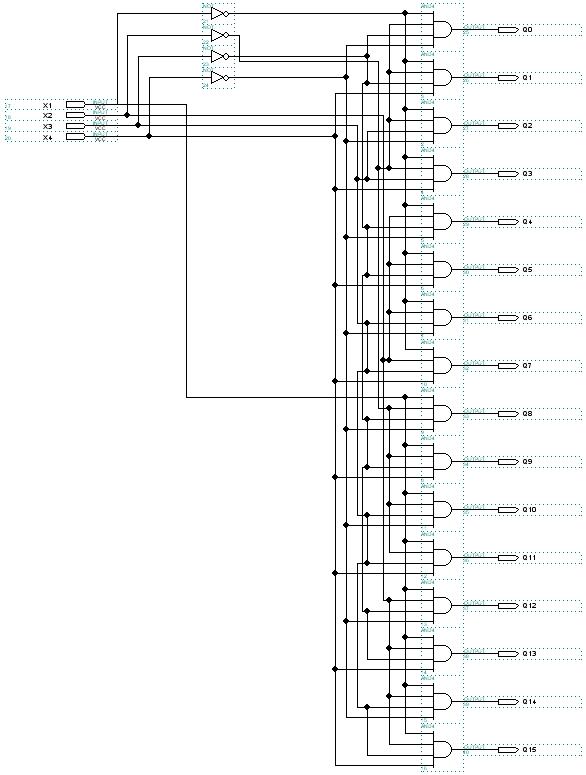

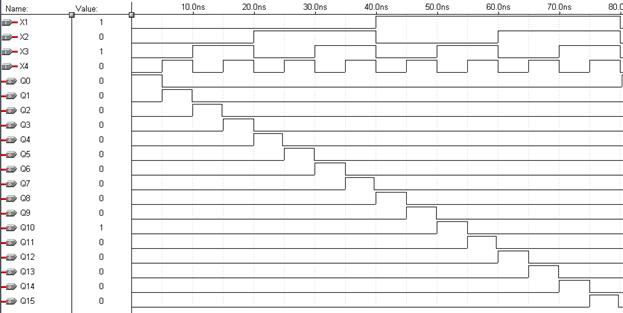

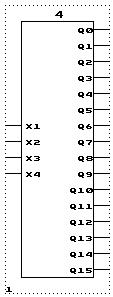

4.Полный дешифратор с активными единичными сигналами на выходе. 15

5.Сборка нового элемента. 19

Выводы.. 21

Список использованной литературы.. 22

Вариант №1

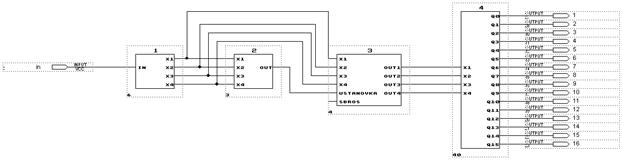

Собрать принципиальную электрическую схему по следующей структурной схеме:

Где:

1. Счетчик -

2. Комбинационная схема –

3. Регистр –

4. Дешифратор –

Произвести моделирование схемы, сняв характеристики работы, и представить в виде завершенного электронного компонента, полученного в САПР МАХ+ (микросхема).

Принципиальные электрические схемы определяют полный состав приборов, аппаратов и устройств (а также связей между ними), действие которых обеспечивает решение задач управления, регулирования, защиты, измерения и сигнализации. Принципиальные схемы служат основанием для разработки других документов проекта: монтажных таблиц щитов и пультов, схем внешних соединений и др.

………………………………………………………………

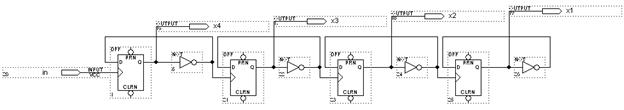

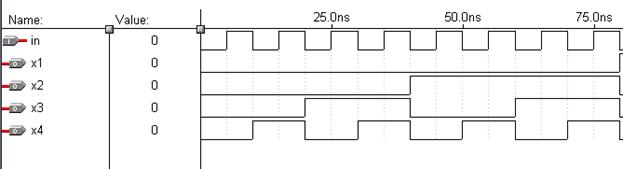

1. Суммирующий двоичный счетчик с последовательным переносом, собранный на D-триггерах

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

………………………………………

Счётчики с последовательным переносом, это счётчики, в которых переключение триггеров разрядных схем осуществляется последовательно один за другим.

Рисунок 1 - Схема суммирующего двоичного счетчика с последовательным переносом, собранного на D-триггерах

Рисунок 2 - Временные диаграммы, характеризующие работу счетчика

Рисунок 3 - Графическое

изображение полученной модели счетчика

Комбинационные схемы - это схемы, у которых выходные сигналы Y = (у1, у2, ..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2,..., хn), поступающих в тот же момент времени t. Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется ………………………………………………………………….

2.1. Построение комбинационной схемы по функции

Таблица 1 –

Таблица истинности для функции  .

.

|

x1 |

x2 |

x3 |

x4 |

a |

b |

c |

d |

e |

f |

g |

h |

i |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

a=

b=

c=a

d=

e=c

f=

g=e f

f

h=

i=g h

h

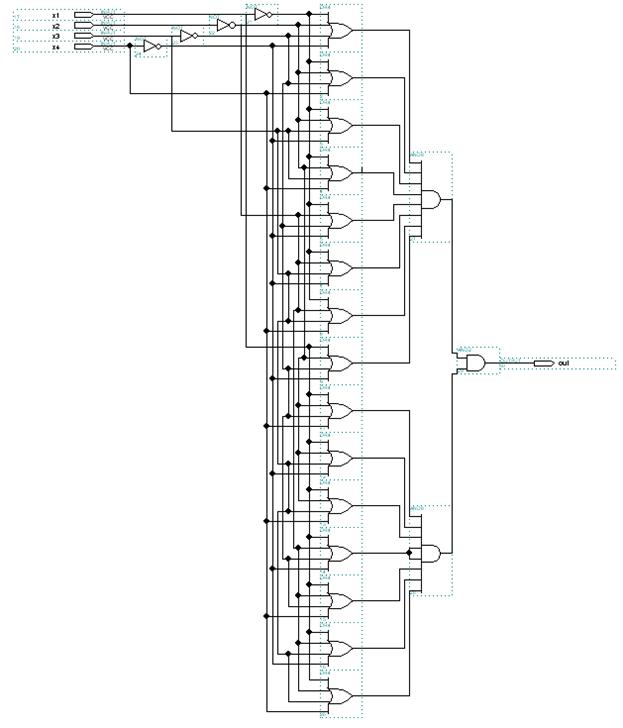

Так как ложных значений у функции больше, чем истинных, то находим КСНФ и по ней строим комбинационную схему (рисунок 4).

Рисунок 4 - Комбинационная схема

Воспользовавшись методом Карт-Карно можно минимизировать эту схему.

|

x3x4 |

00 |

01 |

11 |

10 |

|

|

x1x2 |

|||||

|

00 |

|

|

0 |

0 |

|

|

01 |

|

0 |

0 |

0 |

|

|

11 |

0 |

0 |

0 |

0 |

|

|

10 |

0 |

0 |

0 |

1 |

Рисунок 5 – Сокращение методом Карт-Карно

Рисунок 6 – Сокращённая комбинационная схема

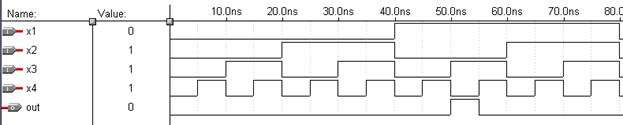

Рисунок 7 - Временные диаграммы, характеризующие работу комбинационной схемы

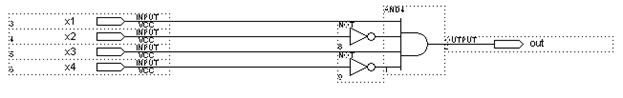

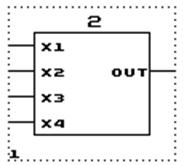

Рисунок 8 - Графическое изображение полученной модели комбинационной схемы

3. Параллельный регистр, собранный на D-триггерахРегистр - накапливающий узел, предназначенный для приема, хранения, преобразования и выдачи двоичной информации.

……………………………………………..

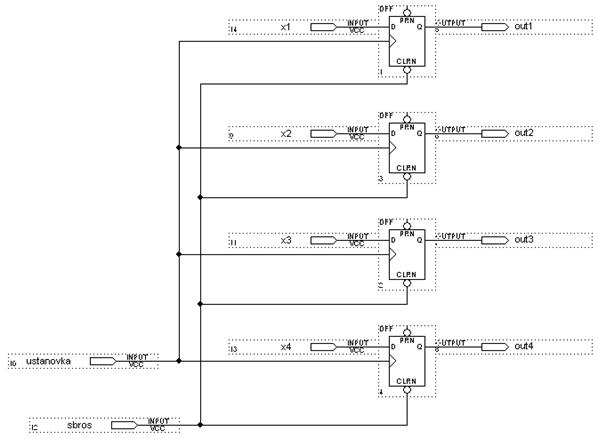

Рисунок 9 - Параллельный регистр, собранный на RS-триггерах

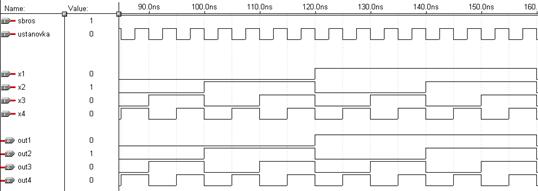

Рисунок 10 - Временные диаграммы, характеризующие работу регистра

Рисунок 11 - Графическое изображение полученной модели

регистра

Дешифратором называется комбинационная схема с несколькими входами и выходами, преобразующая двоичный код, подаваемый на входы, в сигнал на одном из выходов.

………………………………………………………

Таблица 2 - Таблица истинности работы дешифратора

|

x1 |

x2 |

x3 |

x4 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

Y10 |

Y11 |

Y12 |

Y13 |

Y14 |

Y15 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

||||

|

0 |

0 |

1 |

1 |

0 |

0 |

||||||||||||||

|

0 |

1 |

0 |

0 |

0 |

0 |

||||||||||||||

|

0 |

1 |

0 |

1 |

0 |

1 |

||||||||||||||

|

0 |

1 |

1 |

0 |

0 |

0 |

||||||||||||||

|

0 |

1 |

1 |

1 |

0 |

0 |

||||||||||||||

|

1 |

0 |

0 |

0 |

0 |

0 |

||||||||||||||

|

1 |

0 |

0 |

1 |

0 |

0 |

||||||||||||||

|

1 |

0 |

1 |

0 |

0 |

0 |

||||||||||||||

|

1 |

0 |

1 |

1 |

0 |

0 |

||||||||||||||

|

1 |

1 |

0 |

0 |

0 |

0 |

||||||||||||||

|

1 |

1 |

0 |

1 |

0 |

0 |

||||||||||||||

|

1 |

1 |

1 |

0 |

0 |

0 |

||||||||||||||

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

При поступлении на входы дешифратора x1 – x4 четырех разрядный двоичный код преобразуется в сигнал высокого уровня на выходе номер, которого соответствует десятичному значению поступившего кода.

Рисунок 12 - Полный дешифратор

Рисунок 13 - Временные диаграммы, характеризующие работу дешифратора

Рисунок 14 - Графическое изображение полученной модели дешифратора

5.Сборка нового элемента

В этом пункте производится окончательная сборки схемы путем соединения ранее полученных компонентов. От источника сигналов «1» будет поступать напряжение высокого уровня необходимое для нужной работы счетчика и регистра. Счетчик будет производить подсчет импульсов поступающих на его вход «CLKin» от источника. Полученный четырех разрядный код будет поступать на входы регистра и комбинационной схемы. Комбинационная схема будет играть роль фильтра, который будет отбирать …………………………………………………………………………………………………..

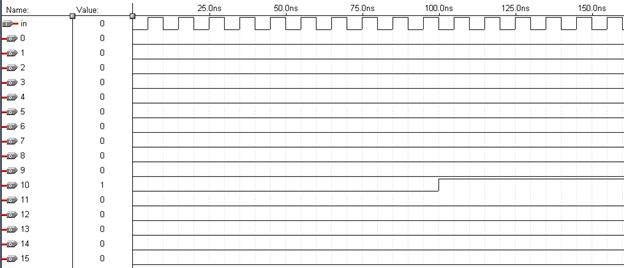

Рисунок 15 - Схема нового элемента

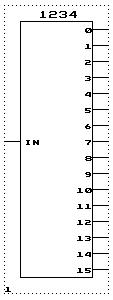

Рисунок 16 - Временные диаграммы, характеризующие работу нового элемента

Рисунок 17 - Графическое изображение полученной модели нового элемента

Выводы

В задачу данного курсового проектирования входило собрать принципиальную электрическую схему, состоящую из 4-х разрядного суммирующего счетчика с …………………………………

элементов.

В ходе выполнения данного проекта были получены знания о работе компонентов используемых в схеме. Так же была освоена программа проектирования устройств на ПЛИС Altera MAX+PLUS II.Были изучены основные методы построения схем из уже имеющихся в библиотеке компонентов, а также получены знания о конструировании своих собственных компонентов.

Список использованной литературы

Основная литература:

1. Потехин Д.С., Тарасов И.Е. Разработка систем цифровой обработки сигналов на базе ПЛИС. - М.: Горячая линия - Телеком, 2007. - 248с.

2. Поляков А.К. Языки VHDL и Verilog в проектировании цифровой аппаратуры на ПЛИС. Учебное пособие для вузов. - М.: Изд. дом МЭИ, 2012. - 220с.

Дополнительная литература:

1. Антонов А.П. Язык описания цифровых устройств. ALTERA HDL. Практический курс.-М.: ИП Радио Софт, 2002.- 224.

2. Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем на микросхемах программируемой логики.-СПб.: БХВ-Петербург,2002.-608 с.

3. Зобенко А. А., Филиппов А. С., Комолов Д. А., Мяльк Р. А.. Системы автоматизированного проектирования фирмы Altera MAX+plus II и Quartus II. Краткое описание и самоучитель. – издательство «РадиоСофт» · 2002 г. · 360 с.

0

0 0

0 0

0 (zip - application/zip)

(zip - application/zip)